Autonomous

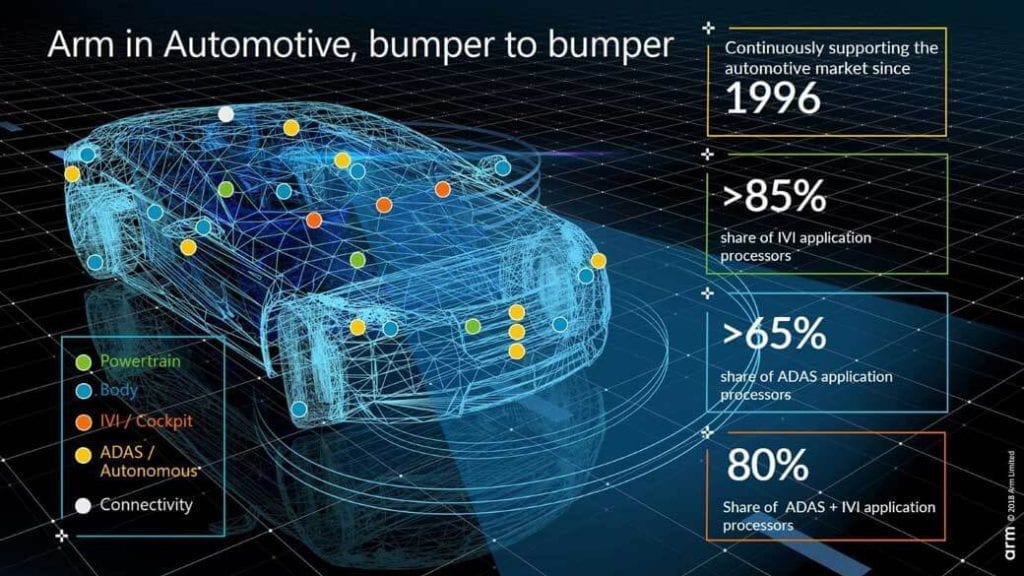

ARM Targets Autonomous Car Technology

Advanced Risk Machine, also known as ARM is a processor architecture based on a 32-bit reduced instruction set (RISC) computer. Licensed worldwide, the ARM architecture is the most commonly implemented 32-bit instruction set architecture. ARM architecture is implemented on Windows, Unix, and Unix-like operating systems, including Apple iOS, Android, BSD, Inferno, Solaris, WebOS, Plan 9 and GNU/Linux.

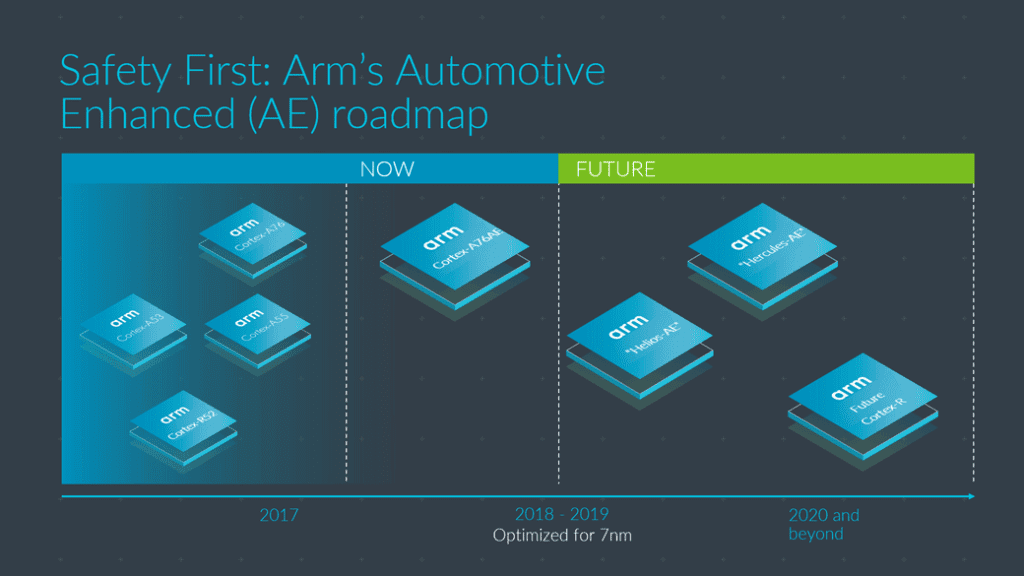

On 26th of September, Wednesday, ARM officially launched an updated processing core called Cortex-A76AE as well as “Arm Safety Ready” for their ecosystem partners in Tokyo, Japan. Both respond directly to the burning need for higher safety requirements in the era of Autonomous Driving and Manuevering utilized in cars, boats, ships and most frequently in aircraft.

Lakshmi Mandyam, the Vice President of the embedded and automotive business at Arm commented on the newly announced development as being, “A simpler and easier way to implement safety,” and “a scalable platform requirement, a foundation of autonomy,” Mandyam noted that Arm is “leading the charge for safety” by creating an easier path for both system developers and chip designers to execute and advance the safety of highly automated vehicles.

The fact remains, however, that some of the leading automotive chip vendors were like SoCs. Nvidia, NXP, Renesas and Intel/Mobileye have already developed, produced and installed their own integrated and dedicated safety features that are used with their own chips; the first three of the lot are using Arm cores and Intel/Mobile on MIPS. So it would not be an over – simplified understatement to say that ARM is a bit late in producing their security system.

ASIL D

“Automotive safety is performed at many levels, including silicon, software, system, and the entire platform,” as per Jim McGregor, tech industry analyst and founder of Tirias Research.

Commenting on the level of safety of the systems thus developed, he added, “The level of safety depends on the applications, but generally you have to ensure a certain level of reliability and failover protection for command and control systems.” As a result, “This goes into the SoC design through secure environments, redundant processing on-chip or between chips, fail-safe instructions, etc. All of this is, then, designed in with the rest of the platform.”

Mike Demler, senior analyst at the Linley Group, commented on how current automotive SOCs comply with the newly developed ASIL ASIL (Automotive Safety Integrity Level) technology: “To support ASIL D in the Xavier SoC, Nvidia, for example, implemented a custom lockstep mechanism and other features,” because ASIL C and D require redundancy. Up till now, Arm supported these automotive requirements with Cortex-R. NXP and Renesas have used those CPU cores in their safety islands.”

Cortex-A76AE

So ARM is launching Cortex-A76AE. What is it?

They describe it as “The industry’s first high-performance application processor with split-lock capability, combining the processing performance required for autonomous applications and high-integrity safety.”

Arm acknowledged that split-lock is “not new to the industry,” but Arm is “the first to introduce it to a processor uniquely designed for high performance automotive applications such as autonomous drive.”

Cortex-A76AE is also designed to optimize the performance of the processor against wattage or power.